- 头条一种基于就地模块的硬件自诊断系统设计导语针对新一代智慧变电站二次系统对就地设备硬件可靠性的要求和硬件全面自检的方法以及内存测试难点,南京南瑞继保电气有限公司、国网湖北省电力有限公司电力科学研究院、国网湖北省电力有限公司的研究人员朱长银、刘东超、夏勇军、黎恒烜、蔡敏,在2020年第7期《电气技术》杂志上撰文,提出一种新的检测方法,以提高内存纠错能力,及时获取硬件设备运行状态。新设计的就地模块具备异常主动预警功能,自动识别二次设备隐性故障,通过通信协议的扩展,把硬件自检信息上送到硬件自检监控系统,实现了变电站二次设备状态的全面感知,为状态检修提供了技术支撑,提高了设备的运行可靠性。该检测方法已在工程中得到实际应用。

新一代智能变电站大量使用一次设备同体设计、紧密耦合的数字化就地模块,因而系统对就地模块等硬件可靠性有很高的要求。硬件设计方面,随着微处理器尤其是现场可编程门阵列(field pro- grammable gate array, FPGA)以及数字信号处理(digital signal processor, DSP)技术的发展,在单一处理器芯片中实现复杂控制和保护功能成为可能,它简化了硬件设计,具有更好的抗干扰性能,有利于提高硬件可靠性。

根据变电站现场运行经验,就地模块靠近一次设备,电磁环境严酷复杂。气体绝缘组合电器设备(gas insulated metal switchgear, GIS)隔离开关操作时,触头间隙会发生预击穿或重击穿放电,产生陡变的行波向两侧传播,遇到波阻抗变化处发生折反射,形成特快速瞬态过电压(very fast transient over-voltage, VFTO)。

在早期采用电子式互感器的智能站中,GIS电子式互感器中的采集器就很容易受到VFTO的影响,具体的干扰波形与不同厂家GIS设备、线路长度、现场接地情况、一次传感器和信号线屏蔽等有关。在贵州某智能站中,电子式互感器采集器受到干扰,曾出现合开关时采样器模数转换芯片误采虚假大电流而出现跳闸,使运行过程中高速数据总线传输的开关量状态异常变位导致保护误动。还有不少电源受浪涌类干扰而出现损坏的情况。

受电子元器件的老化、一次设备高电压冲击等因素的影响,保证数字化就地设备的硬件永远不损坏是实现不了的。要提高硬件可靠性,就必须具有硬件自检功能,在装置的调试和运行过程中能及时发现硬件故障,保证装置不误动并能立即报警,通过系统综合决策,在最短时间内采取措施予以修复。

国内几大二次设备厂家的装置都具备硬件自检和互检能力,比如继电器、开入的智能化检测以及对容易损坏的电源电压输出质量的测量、温度综合监测等。但目前的硬件检测也有不足,比如FPGA软错误、内存(RAM)软错误等问题并不容易被检测,从而引发电力系统事故造成损失。

半导体器件发生单粒子效应时,其危害包括数据丢失、功能中断等。如在CPU的指令缓存中引起软错误(soft error),则将导致CPU不能执行预期的功能。超级计算机的软错误曾造成美国Los Alamos国家实验室重大损失。随着芯片半导体尺寸的减小和存储容量的持续扩大,静态存储器(SRAM)或者片外的动态存储器(DRAM)单逻辑位的软错误概率(soft error rate, SER)呈指数级增长。

本文研究硬件全面自检的方法,及时获取硬件设备运行状态,实现变电站二次设备状态的全面感知,从而保证就地模块设备可靠运行。

1 硬件自检架构

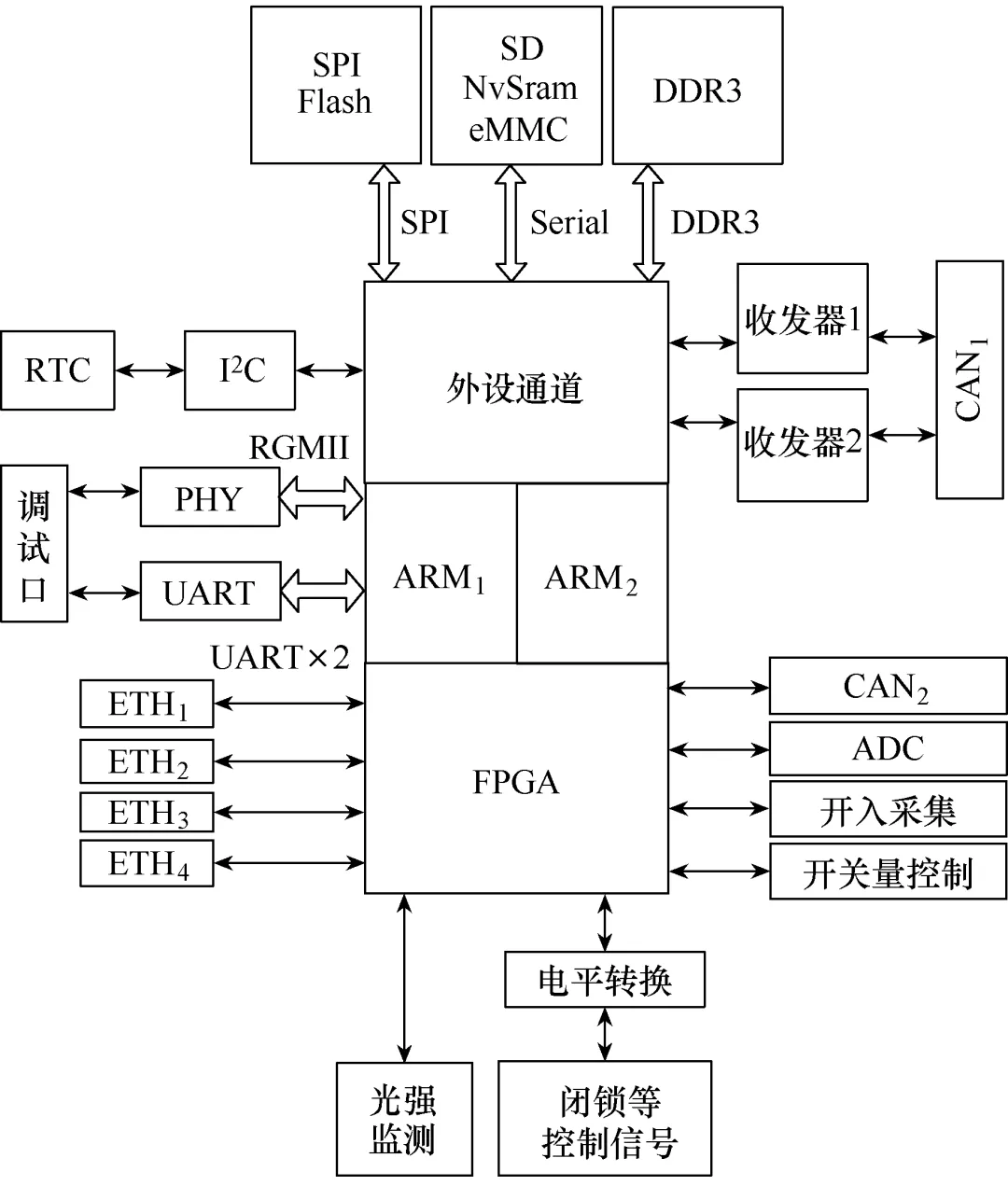

就地模块硬件(其架构如图1所示)采用系统级芯片(system on chip, SOC)(A9双核800MHz,FPGA LC125K),支持256MB内存和丰富的存储设备。采用16位模数转换器(ADC),支持网络口(ETH)、CAN总线、I2C总线扩展,面板支持4路网口、对时口等。

1.1 自检设计分类

自检设计分类是从产品设计角度来研究处理系统故障,对硬件进行自检设计,将可能发生的故障根据成因和功能电路进行分析和分类。

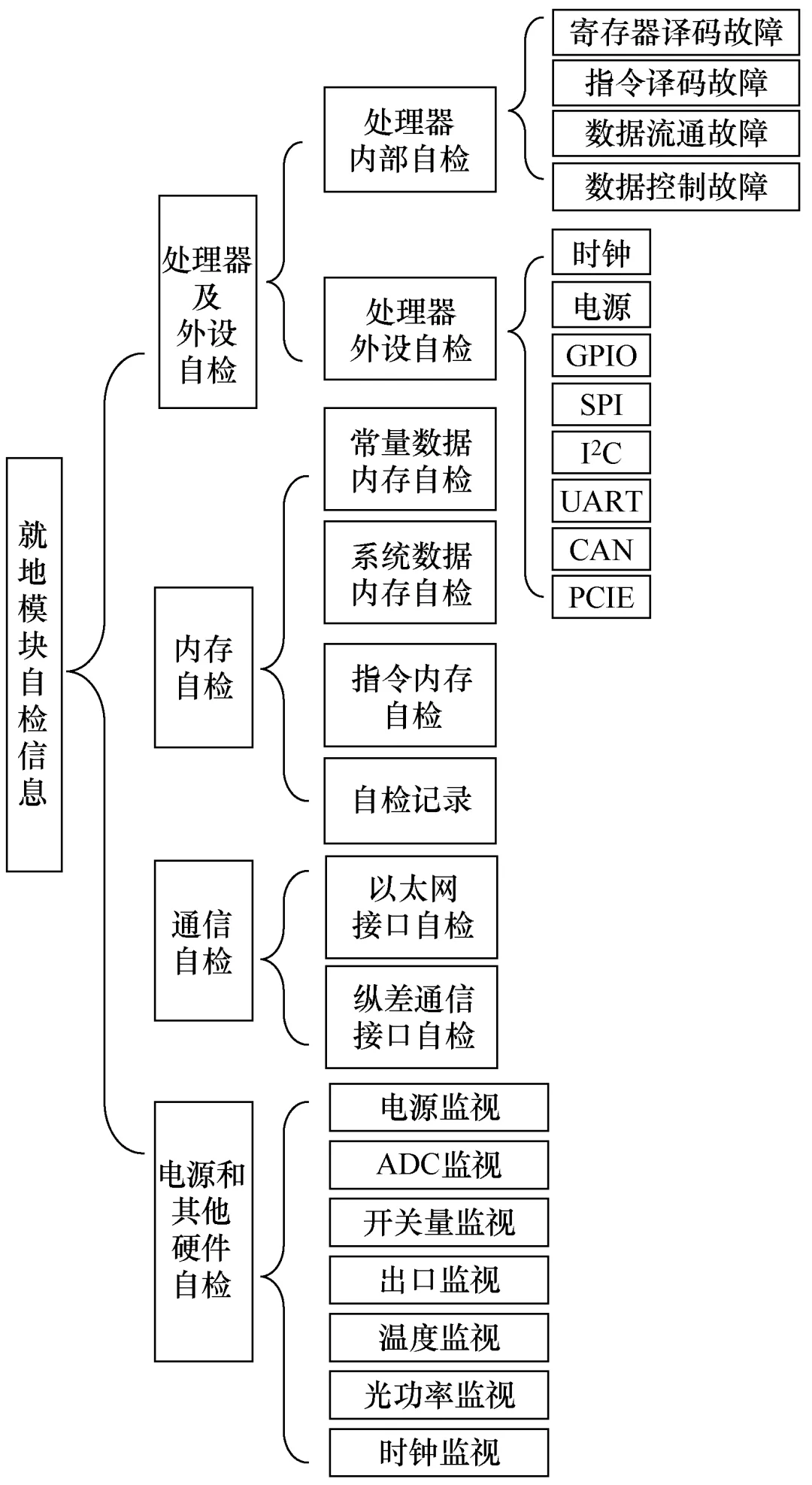

就地模块硬件自检的信息主要来自外设,包括处理器及外设自检、内存自检、通信自检、电源和其他硬件自检等。其分类如图2所示。

图1 就地模块硬件架构

图2 就地模块硬件自检信息分类图

1.2 自检设计的实现

硬件自检的难点主要在处理器和内存,其关系到应用功能的运行可靠性。

1)处理器及外设自检设计

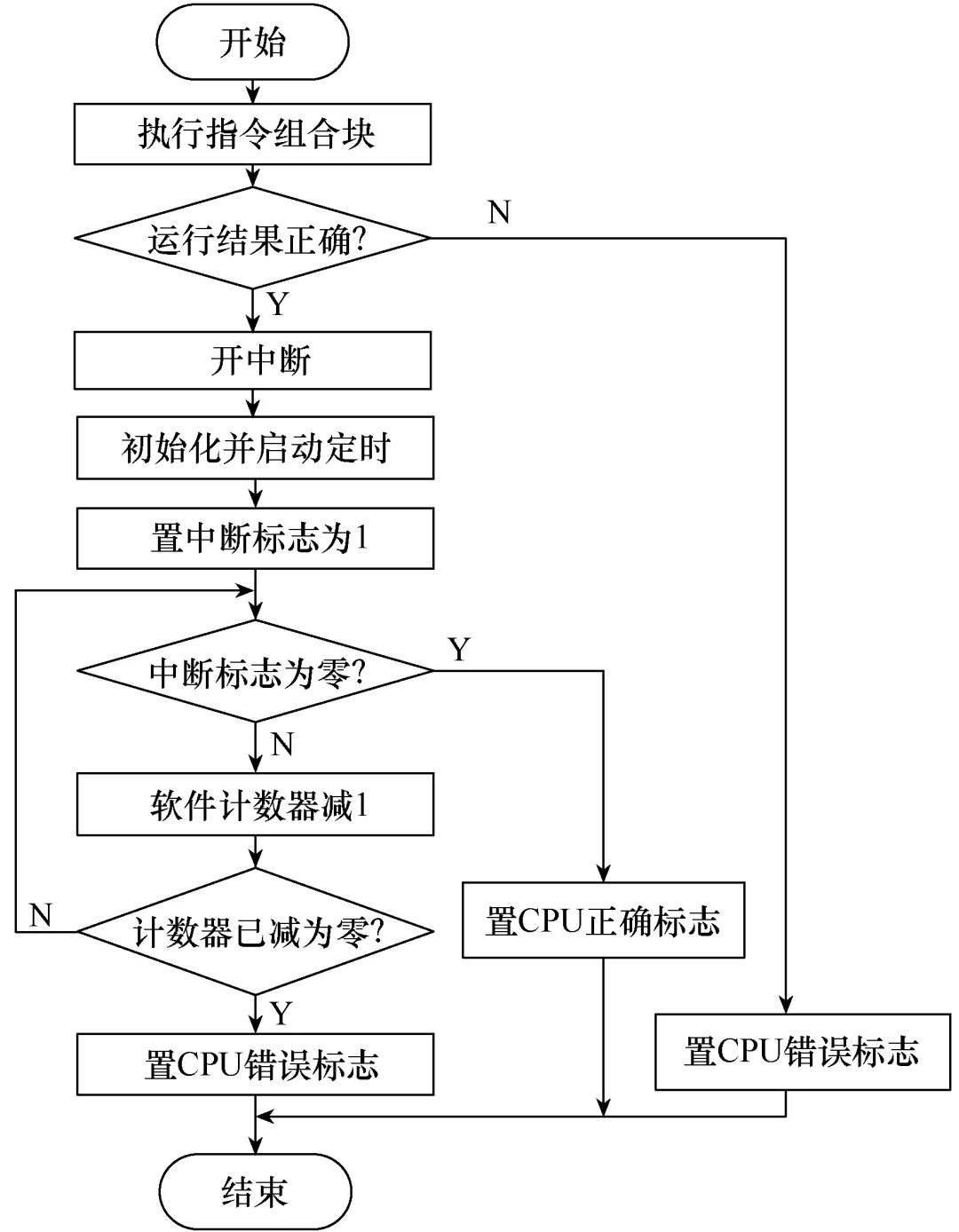

处理器(DSP、SOC等)的特点是速度快、结构复杂、可观察性低。本文对处理器的自检从处理器的功能实现出发,对不可见的复杂功能电路进行故障分析。通过设计将运算指令、传送指令、跳转指令、逻辑指令等组合为完成一定运算功能的指令块,利用该指令块的结果判断处理器的传输、计算、输出等功能。

检查处理器是否能够正确执行全部指令,并且可以在定时器中断中清除中断异常标志,来检查处理器的中断和定时器功能是否正常。

处理器内部自检流程如图3所示。

图3 处理器内部自检流程图

装置上电后,执行预先的指令块,利用该指令块的结果判断CPU的传输、计算、输出等功能,如果运算结果与存储正确值不一样,设置CPU错误标志;如果结果一致,就继续进行处理器中断和定时器功能检测。

若在规定时间内中断程序中的异常标志被清零,则置CPU自检成功;若超过规定时间中断程序中的异常标志依然存在,则设置CPU自检错误。

处理器外设自检通过监视接口模块寄存器状态、输入、输出数据互相校验,采用通信接口发送、接收自环检测等方式自检。

2)内存自检设计

内存自检用于解决运行过程中内存意外出错的问题,以有效防止因存储器出错导致的程序逻辑异常。内存自检包括数据内存自检(如保护定值、系数表、关键全局变量、指针等)和指令内存自检(如运行过程中RAM代码等)。

处理器运行时,RAM中存储的信息主要包含程序代码和数据两大类,其中代码属于只读属性,在运行过程中被处理器读取并执行,内容不会被修改。数据在运行过程中可能部分会被修改覆盖,还有部分是只读状态,会一直保持不变。对于运行过程中保持不变的代码空间和部分数据空间,采用多存储器的相互校验机制进行监视检查和出错恢复。

图4 内存自检架构图

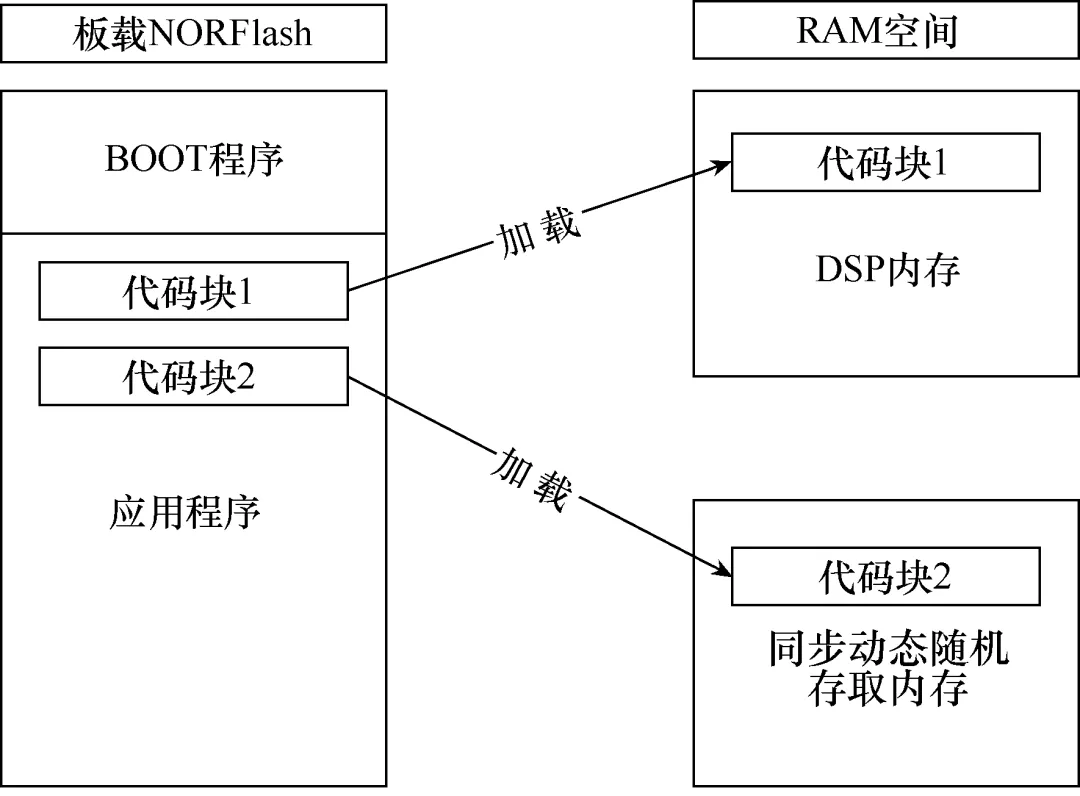

嵌入式板卡上的程序文件一般存储于Flash中,分为BOOT引导程序和应用程序,板卡上电后,处理器从BOOT引导程序开始执行,把Flash中的程序块解析后载入到不同的内存区域,完成该步骤后自动跳转应用程序,并开始执行。

Flash中只读状态的程序在内存中形成了备份,程序运行过程中,将内存中导入程序与Flash中的源程序代码进行实时比较,监视内存中的代码区域是否发生了软错误,再进行记录以及纠错。

根据对源程序在不同物理介质进行备份、互校的机制,本文提出一种程序、数据多重备份、互校的软错误处理办法。在继电保护装置中,跳闸门槛、瞬态电流等可能会引起装置拒动作或误动作,嵌入式板卡处理器运行时,处理器根据程序和数据区的重要程度,将待监视的程序及数据在动态RAM空间分配相同大小的区域,将源程序和数据进行双重备份。

备份程序及数据运行之前,首先将源程序和数据与两块备份区域进行三者校验,若三者一致,则判断程序、数据正确,载入运行。根据半导体器件发生单粒子效应的特点,内存出现软错误时,不一致的区域很容易被对比发现,若两个区域相同,第3个区域不同,则借鉴继电保护逻辑中一项“三取二”的思想,用一致的两个区域来纠正第三个区域;若3个区域都不相同,则可认为发生了超出预知的错误,判断程序、数据有运行风险,采取处理器复位重起的方式来确保安全性。

当系统监视检测到内存异常时,会记录到本板非易失性存储器中。具体内容包括异常发生时间、正确的数据、错误的数据、异常地址、异常地址附近的内容等。异常记录被存放于板卡非易失性存储器中,可以通过调试工具上招,便于异常分析。

现场应对内存出错采取的措施一般是软重起,以便使系统能够尽快恢复运行。获取到内存出错标志后,首先闭锁装置,然后做内存出错报文。若当前检测轮次大于3次,则重起处理器。

1.3 自检系统可靠性

硬件自检系统除了本身需要完备的功能以检测主要硬件故障外,还需要保证自检系统工作可靠运行。在设计系统时,应考虑当故障自动被检测出不安全状态时,系统能做出正确响应。设计故障检测的优先级结构及安全性控制、校正逻辑、处理和响应故障的模块,产生对硬件进行自主控制信号,能直接影响硬件部件运行或启动安全关键功能。

硬件自检系统可靠机制主要体现在软硬件结合处理方面,包括电源失效防护、加电检测、电磁干扰、系统不稳定、接口故障、干扰信号、错误操作等设计。

硬件加电的瞬间,电源可能出现间歇故障,系统或因电源上电过程的抖动或上电顺序不一致而出现运行问题,此时需软硬件配合处理这两种状态下的潜在不安全初始状态,提供安全的关闭措施,使电源有波动时的系统不会产生潜在的危险。系统加电的过程,软件对系统进行检测,验证系统安全且在正常运行;软件还对系统进行周期性检测,以监视系统的安全状态。

对于电磁干扰、宇宙重粒子的冲击,硬件设计应将这些干扰控制在电磁兼容(electromagnetic compatibility, EMC)规范之下,软件设计要使得在出现这种干扰时,系统仍处于安全状态。当外来干扰使系统出现不稳定、不宜继续执行指令时,软件应有等系统稳定后再执行指令的措施。

软件应能判断输入操作正确(或合理)与否,并在遇到不正确(或不合理)输入和操作时拒绝该操作的执行,并进行提醒或报警,同时给出错误的类型和纠正措施。

2 自诊断系统的通信

自诊断系统通信架构的功能是将就地模块的自检信息通过站控层上送到监控系统,对保护运行状态进行远程监视,并编制保护运行状态评估信息(以下简称保信)上送方案。

系统选用的过程层设备为电磁式互感器电压电流就地模块,程序实现其硬件全面自检后,从光口发出含自检信息的面向通用对象的变电站事件(generic object oriented substation event, GOOSE)报文。

站控层选用支持GOOSE功能的PCS-9705A-D型号测控,接收就地模块的自检信息并搬运到站控层网络,通过站内制造报文规范(manufacturing message specification, MMS)通信上送到后台,最后由子站汇集整理所有监视设备的全信息,并以系统工程测试程序(system engineering test program, SFTP)方式推送到保信主站,如图5所示。

图5 状态信息上送架构图

基于硬件平台分析发现了可能出现的不同程度装置的运行故障,针对这些故障提出了硬件自诊断的算法或判定逻辑。

数据对象引用名便于理解自检信息在icd文件中的模型配置。自检信息包括信号量和模拟量:①信号量动作时表示出现自检告警,复归表示告警消失;②模拟量可以实时监测其变化过程和趋势。各信号对应的自检信息分类见表1右侧所示。

系统模拟两层一网简化架构,通信符合现代61850数字化站的要求,过程层使用GOOSE通信,站控层使用MMS通信。

3 自诊断系统的实现

就地模块一旦发生自检告警,就会通过GOOSE协议发送给测控装置,由测控装置转成MMS上送。为实现以上站内通信,整理就地模块二次自检信息,统计有意义的信号,在应用层完成这些自检信号的变量定义,根据相关内容完成逻辑判断,实现对应功能,完成GOOSE文本及icd文件的配置,符合61850通信规范,导出供工程配置使用,搭建硬件平台,进行工程配置,搭建实例化展示系统(如图6所示)。

图6 实例化展示系统

国家电网公司国内首座半户内智慧变电站——湖南某智慧变电站已于2019年年底正式投入运行。该站使用南瑞继保公司的就地设备具备异常主动预警功能,自动识别二次设备隐性故障,若发现设备异常则主动预警,实现了变电站二次设备状态全面感知,为状态检修提供了技术支撑。

4 结论

本文针对新一代智能变电站二次系统对就地设备硬件可靠性的要求,研究硬件全面自检的方法,及时获取了硬件设备运行状态,通过通信协议进行扩展,将硬件自检信息上送到硬件自检监控系统(如图7所示),为检修等工作提供信息数据,提高了设备运行的可靠性,为运维检修工作带来了便利。

图7 监控系统自诊断信息图

电厂关键技术研究及其应用”专题征稿通知.jpg)