- 头条《电工技术学报》优秀论文|抑制SiC MOSFET桥臂串扰的改进门极驱动设计导语传统驱动下SiC MOSFET受高开关速度特性及寄生参数影响,桥臂串扰现象更加严重,而现有抑制串扰驱动电路又会增加开关损耗、开关延时和控制复杂程度,本文结合驱动阻抗控制与负压关断的串扰抑制方法,提出一种改进门机驱动电路。试验结果表明,相比典型抑制串扰驱动电路,提出的驱动方法在有效抑制串扰的同时,减小了开关损耗与开关延时。

《电工技术学报》2019年度优秀论文获奖论文简报

《光伏发电出力预测技术研究综述》等15篇优秀论文入选《电工技术学报》2019年度优秀论文,荣获中国电工技术学会表彰。现将部分获奖论文的文章简报分享给各位读者,以期促进本领域的技术交流。

传统驱动下SiC MOSFET受高开关速度特性及寄生参数影响,桥臂串扰现象更加严重,而现有抑制串扰驱动电路又会增加开关损耗、开关延时和控制复杂程度,本文结合驱动阻抗控制与负压关断的串扰抑制方法,提出一种改进门机驱动电路。试验结果表明,相比典型抑制串扰驱动电路,提出的驱动方法在有效抑制串扰的同时,减小了开关损耗与开关延时。

团队介绍

重庆大学李辉教授研究团队主要围绕可再生能源电力装备安全可靠运行开展研究,拥有完备的材料-封装-器件-装备仿真及实验平台。近五年,团队在大功率电力电子器件可靠性研究方向承担了国家自然科学基金智能电网联合基金重点项目1项“压接型IGBT器件封装老化失效演化机理及测评方法”,参与国家重点研发计划项目3项“电力系统用国产高压大功率IGBT芯片及模块的应用研发”、“碳化硅大功率电力电子器件及应用基础理论研究”、“大容量电力电子装备多物理场综合分析及可靠性评估方法研究”;承担国家自然基金面上项目2项,参与工信部高新技术科研项目1项,国际合作项目2项以及省部级科技项目10余项;获重庆市科技进步二等奖、三等奖各1项。

李辉

1973出生,教授,博士生导师,教育部新世纪优秀人才支持计划入选者,爱思唯尔“中国高被引学者”,输配电装备及系统安全国家重点实验室副主任,中国电机工程学会电力电子器件专业委员会委员,中国工业节能与清洁生产协会绿色电机系统专业委员会专家,IET Renewable Power Generation副编辑。主持国家自然科学基金重点项目1项、面上项目2项,参与国家重点研发计划项目2项和国际合作项目2项,获重庆市科技进步二等奖1项(第一完成人),发表高质量学术论文72篇,出版专著1部,授权国家发明专利16件,申请发明专利11件。主要研究方向为电力电子器件封装与可靠性、风力发电技术、特种电机系统设计与控制。

黄樟坚

1992出生,硕士研究生,研究方向为SiC电力电子器件驱动设计及应用。

研究背景

近年来,以碳化硅(Silicon Carbide, SiC)MOSFET 为代表的宽禁带半导体器件因其具有高开关频率、高开关速度、高热导率等优点,已成为高频、高温、高功率密度电力电子变换器的理想选择。然而随着SiC MOSFET开关速度加快,桥式电路受寄生参数影响加剧,串扰现象更加严重。由于SiC MOSFET 正向阈值电压与负向安全电压较小,串扰问题引起的正负向电压尖峰更容易造成开关管误导通或栅源极击穿,进而增加开关损耗,严重时损坏开关管。

论文方法及创新点

提出一种在栅源极增加三极管串联电容新型辅助支路的改进驱动设计方法,该方法具有开关损耗小、延时较短、控制简单的特点。论文首先阐述串扰现象的产生原理及其典型抑制方法,其次分析改进驱动电路工作原理与关键参数设计原则,最后,搭建双脉冲实验平台,对改进驱动电路有效性进行实验验证。

改进抑制串扰驱动电路的思想是在串扰产生过程中,通过控制三极管开断,使三极管串联电容的辅助支路为米勒电流提供旁路通道,降低栅极驱动回路阻抗,抑制串扰,同时减小辅助支路电容对 SiC MOSFET开关特性的影响,其原理图与相关开关波形如图1、图2所示。

图1 改进抑制串扰驱动电路

图2 改进驱动电路相关波形

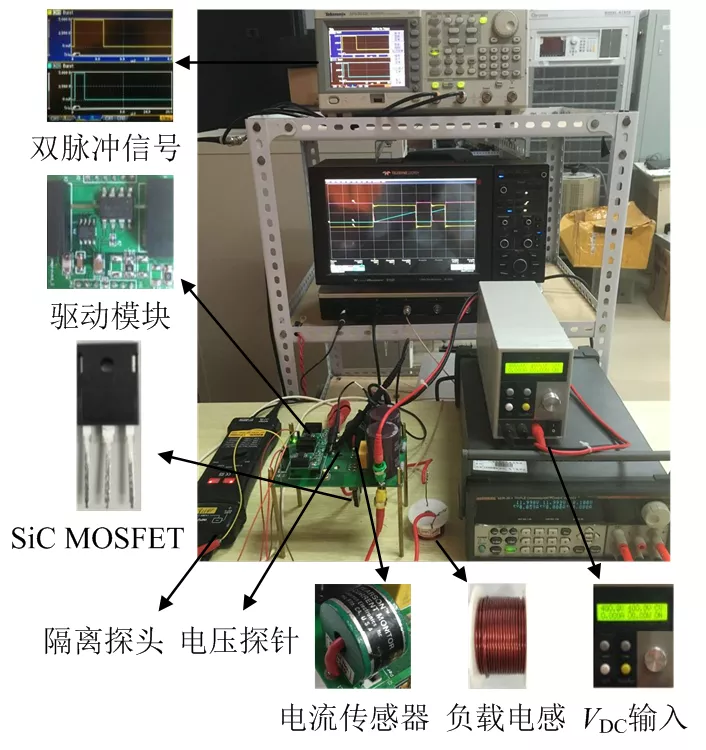

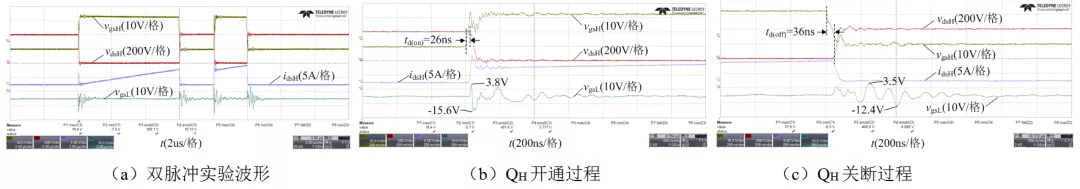

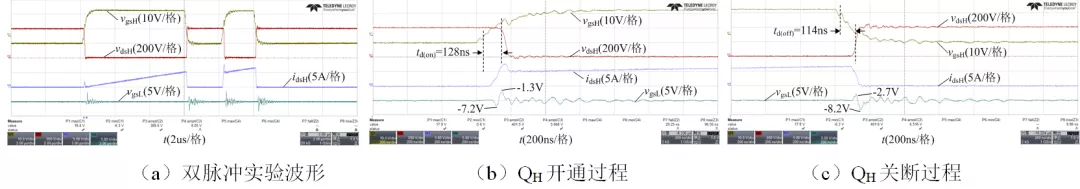

为了验证改进抑制串扰驱动电路的有效性,本文基于 SiC MOSFET 器件 C2M0080120D,搭建了如图3所示的双脉冲测试实验平台,并对传统驱动电路、典型抑制串扰驱动电路、改进抑制串扰驱动电路进行了实验对比。图4给出了改进抑制串扰驱动电路原理,图4~图6分别给出了驱动电阻为10Ω,输入电压为400V,负载电流为5A时,不同驱动电路的实验波形。

图3 双脉冲测试实验平台

图4 传统驱动电路实验波形

图5 典型驱动电路实验波形

图6 改进驱动电路实验波形

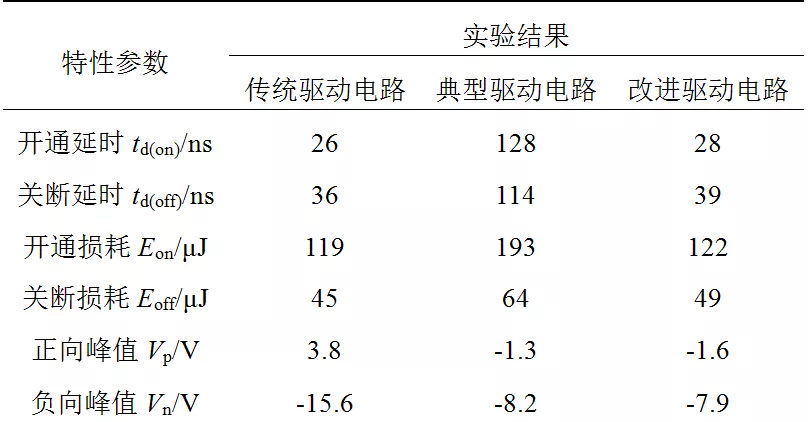

不同驱动电路实验对比结果如表1所示。

表1 不同驱动电路实验对比结果

结论

为了有效解决典型驱动电路在抑制串扰同时增加开关延时与开关损耗问题,本文提出了一种在SiC MOSFET栅源极增加三极管串联电容新型辅助支路的改进抑制串扰驱动电路及其设计方法,并通过原理分析与实验验证,表明了所提改进串扰抑制驱动电路及其参数设计方法的有效性。所得主要结论如下:

①传统无辅助支路的SiC MOSFET驱动电路,桥臂串扰现象明显。典型抑制串扰驱动和本文所提改进驱动电路都能有效抑制串扰问题。

②无论是典型抑制串扰驱动电路,还是本文提出的改进驱动电路,SiC MOSFET开关损耗都会随驱动电阻、输入电压、负载电流的增大而增加;而SiC MOSFET开关延时受输入电压与负载电流影响相对较小,但也会随驱动电阻的增大而增加。

③相比典型抑制串扰驱动设计,本文所提改进驱动设计有效降低了开关延时与损耗,且随着驱动电阻、输入电压、负载电流增大,降低SiC MOSFET开关损耗的效果更明显,进一步说明本文所提方法在抑制串扰和提高开关特性方面更具优势。

引用本文

李辉, 黄樟坚, 廖兴林, 钟懿, 王坤. 一种抑制SiC MOSFET桥臂串扰的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285. Li Hui, Huang Zhangjian, Liao Xinglin, Zhong Yi, Wang Kun. An Improved SiC MOSFET Gate Driver Design for Crosstalk Suppression in a Phase-Leg Configuration. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

电厂关键技术研究及其应用”专题征稿通知.jpg)